|

It pulls 84W under max load, a decent low profile cooler will do fine, never mind towers. People just freak out whenever a CPU goes over 60C�

|

|

|

|

|

| # ? May 18, 2024 06:39 |

|

Yeah I have mine under a Dark Rock TF 2 and it does amazing, way better than I expected when I initially bought it. (Running -20 on all cores)

|

|

|

|

speaking of cooling, do i need to add 10c to my fan curve in asus bios? pretty sure this thing triggers 10c above where it should with my fan speeds matching the 80c point rather than 70c, but setting my non-idle points to 80c and 90c is a bit excessive otherwise i can never remember how you're supposed to set that stuff i forgot why i stopped using fancontrol; then i set it up, and it broke my cpu_fan bios driver, and i suddenly remembered kliras fucked around with this message at 19:00 on Sep 12, 2023 |

|

|

|

kliras posted:speaking of cooling, do i need to add 10c to my fan curve in asus bios? pretty sure this thing triggers 10c above where it should with my fan speeds matching the 80c point rather than 70c, but setting my non-idle points to 80c and 90c is a bit excessive otherwise First and 2nd gen ryzens did a thing where CPUs ending in X had a +10C offset on the main reporting temp, but I'm pretty sure that stopped long ago. Do you have hysteresis / ramp delay set on the fans? kliras posted:i can never remember how you're supposed to set that stuff There's no one right way to do it. The defaults are made to work for the stock coolers, and so are usually pretty aggressive about spinning up because those don't have a lot of thermal mass. For aftermarket coolers you can up the temperature points or drop the speeds in some combination. Otherwise, every combination of CPU cooler, fan, system, and person will have a different idea of what's best.

|

|

|

|

Klyith posted:First and 2nd gen ryzens did a thing where CPUs ending in X had a +10C offset on the main reporting temp, but I'm pretty sure that stopped long ago. this x470 asus motherboard is a mess already, but i'm just wondering what the logic here. the reasons my fans were louder than i thought doesn't appear to be because of hysteresis or even thermals but because it uses the stress mode for 80c and this is after a fresh repaste on the d15 and reinstall of the bios to fix the cpu_fan bios driver maybe i'll try out fan xpert, having exhausted all the alternatives

|

|

|

|

5800X3Ds can spike hot. Don't worry about it.

|

|

|

|

Stanley Pain posted:5800X3Ds can spike hot. Don't worry about it. Mine sure loves to do that. I've paired it with a noctua D12L and it likes to average/just hang out at the high 70s to 80 for BG3 set at 120fps when in conversations without undervolting. Haven't actually checked with doing that yet. I don't really understand how to use core cycler or other things to test an undervolt (and just setting it to -30 had it crash after a couple hours of ff14 so I turned that down to -15 for now. If it ever crashes again I'll just drop it to -10 or turn it off altogether.

|

|

|

|

Core Cycler is easy. Just let it run overnight every night or while you are at work for like a week. If it reports an error on any core, then the undervolt is too aggressive. It is highly annoying, though. I understand. I hated having to do it and just gave up on undervolting altogether because I valued stability more, especially since my machine is my WFH machine.

|

|

|

|

VorpalFish posted:There's been a lot of talk about igpu cannibalizing the low to midrange GPU market though, and that's going to need bandwidth if it's going to happen. That's supposedly what Strix Point/Strix Halo APU's are supposed to address, albeit I suspect they'll at least start out as high-end notebooks. A 256bit LPDDR5 interface to on-package memory for ~270GB/sec bandwidth on the Halo would somewhat address the bandwidth issue, albeit would still need some infinity cache to not be a bottleneck.

|

|

|

|

gradenko_2000 posted:Finally, a CPU that can run C�ntinuum: roleplaying in The Yet Lmao this was good Been running my 7800x3d for two weeks now, replacing my heater of a 9900k. I only have a 2080 Ti but I didn�t realize how much of a bottle neck the 9900k has become when it came to frame time. The stuttering is all gone in games like Baldurs Gate 3 and COD MW2. I was so used to the era where you could keep your cpu for 5 years (got the 9900k late 2018) and not be too far behind. I didn�t think I�d get this much of a gain

|

|

|

|

MagusDraco posted:Mine sure loves to do that. I've paired it with a noctua D12L and it likes to average/just hang out at the high 70s to 80 for BG3 set at 120fps when in conversations without undervolting. Haven't actually checked with doing that yet. kliras fucked around with this message at 10:33 on Sep 13, 2023 |

|

|

|

Curve optimizer undervolts are far more likely to cause instability in idle or light load situations than in full loads. I'm not really sure how good core cycler is at finding that type of instability.

|

|

|

|

Dr. Video Games 0031 posted:Curve optimizer undervolts are far more likely to cause instability in idle or light load situations than in full loads. I'm not really sure how good core cycler is at finding that type of instability. Core cycler loops single thread Prime95 and switches affinity between cores to test peak single core boost, I don't think it'll catch idle/sleep state instability

|

|

|

|

Dr. Video Games 0031 posted:Curve optimizer undervolts are far more likely to cause instability in idle or light load situations than in full loads. I'm not really sure how good core cycler is at finding that type of instability. The thing that makes you crash from undervolt is transitions between high and low power consumption. The root problem is the CPU can change power use far faster than the VRM can change supply. During that interval your voltage goes off from the target -- load high to low you get overshoot, low to high you get undershoot. Both are bad, undershoot causes crashes and overshoot can age or destroy silicon. So the system is calibrated low by default, with just a little bit of margin to cover CPU variance. This is why you can safely overvolt a CPU by a lot more voltage than you can undervolt. Offset undervolts are working with "how much better is my CPU than the worst case CPU that still passes QC?" Undervolts cause crashes in low & light load because you have lots of very brief spikes in CPU load when you're doing stuff like loading webpages or whatever. You notice them more because the average person spends way more time running light. But the best way to produce them is some artificial process to flick rapidly between high and low power use. Core cycler moves a workload between cores and periodically does short suspends of the processes. That produces a lot of high-low transitions. I don't know that it's the best way -- you could also try running prime95 with max power across all cores and wiggle the mouse. But it seems decent.

|

|

|

|

When I was initially undervolting and load testing I definitely ran into low load crashes that core cycler or prime95 didn't catch, took a while to figure out the negative offset each core would take. Then I updated bios and didn't take a screenshot of what I had each core set too....so I just do a flat -20, instead of a range from -30 to -20. Took probably a couple weeks of off and on testing, while occasionally running into low load crashes. Not looking to go through that much work again, even though most of it was just setting up stuff to run in idle time.

|

|

|

Arzachel posted:Core cycler loops single thread Prime95 and switches affinity between cores to test peak single core boost, I don't think it'll catch idle/sleep state instability

|

|

|

|

|

Alright, THIS looks like it might be the next Steam Deck killer. https://www.youtube.com/watch?v=zd6WtTUf-30 Take one Framework mainboard, build into an enclosure with controllers, and you've got a steam deck you can upgrade or hand-me-down hardware into. A ROG Ally is already $700, and the AMD 7840U Framework mainboard is also $700... but upgradable and replacable.

|

|

|

|

I will have a spare Framework main board (albeit Intel 11th I think) once I get the new one, but the rest of the build is beyond me. Alas!

|

|

|

|

Subjunctive posted:I will have a spare Framework main board (albeit Intel 11th I think) once I get the new one, but the rest of the build is beyond me. Alas! The maker of that does say they will be offering a kit for the conversion. I wish they would opensource the plans though. Screen, battery, controllers, and speakers could be sourced rather easily. A case could be sourced or 3d printed. Since the framework setup is pretty much all-in-one, I'd guess the most work would be battery, video, and speaker connections and mounting. They said the controllers are bluetooth.

|

|

|

|

That�s the worst screen to body ratio I�ve seen since like 2005.

|

|

|

|

Perplx posted:That’s the worst screen to body ratio I’ve seen since like 2005. Crumple zones

|

|

|

|

Dr. Video Games 0031 posted:Curve optimizer undervolts are far more likely to cause instability in idle or light load situations than in full loads. I'm not really sure how good core cycler is at finding that type of instability. It doesn't test well for "will audio crackle" or other extremely sensitive cases. My 7800x3d is technically stable with an all core -20 (hundreds of hours of core cycler/other tests, gaming, etc), but audio is inconsistent and will crackle randomly. It's especially tedious because I can't isolate it to a core to figure out if some cores need different values. I set tjmax to 80 and all core to -12 and it seems fine, tempted to try -20 again with the 80 tjmax. My motherboard was setting 85 tjmax and this can cause crackling/etc according to oc enthusiasts even if it never shows at 80c or higher in monitoring tools. With 85 tjmax I needed -5 for no crackling. Khorne fucked around with this message at 17:18 on Sep 19, 2023 |

|

|

|

cyberpunk 2077 2.0's new eight-core utilization is going to be a fun new stress test

|

|

|

Khorne posted:It doesn't test well for "will audio crackle" or other extremely sensitive cases. My 7800x3d is technically stable with an all core -20 (hundreds of hours of core cycler/other tests, gaming, etc), but audio is inconsistent and will crackle randomly. It's especially tedious because I can't isolate it to a core to figure out if some cores need different values. BlankSystemDaemon fucked around with this message at 19:16 on Sep 19, 2023 |

|

|

|

|

audio crackle can also happens if you set your buffer size too high in your audio interface settings

|

|

|

|

BlankSystemDaemon posted:I assume you've checked your deferred procedural calls and interrupt service routines using LatencyMon? * might be a combination of things due to hand-tuned memory, voltages, infinity fabric, etc, but I have things stable except when I mess with curve optimizer so I'm okay with blaming it on co. The solution to a stable -20 with no audio crackling could be adjusting vsoc/vddp/etc voltages, but I'm not really sure that's true given without negative co the current ones aren't a problem. kliras posted:audio crackle can also happens if you set your buffer size too high in your audio interface settings I have it seemingly stable right now with -12 on co and 96khz & 192 buffer size. It's stable at this same settings with -5 co also (& at 128 / 256 / 512 buffer sizes), and that one is 24/7 stable with no audio issues. I only rebooted yesterday with -12 & 80c tjmax instead of 85 so I'm not sure yet if things are truly okay or if I'll get a 1/4th second crackle while watching a 30 minute video or something. -20 with 85tjmax got pretty bad when the system was under load with crackling on all sounds playing but the mic still being crystal clear. Adjusting buffer size didn't really seem to help while it was happening. Setting frequency to 44 & adjusting buffer size might have helped, but the issue with that is it introduces significant latency to my final microphone output even if my interface drivers say it should have the same latency due to a smaller buffer. Khorne fucked around with this message at 20:33 on Sep 19, 2023 |

|

|

Khorne posted:yes, the issue is related entirely* to undervolting the cpu through curve optimizer. If I set it to -5 or turn it off my audio is perfect. Does it happen using PCI, or USB, or both?

|

|

|

|

|

BlankSystemDaemon posted:Out of curiocity, what kinda audio interface are you using? I have game mode off & all usb power saving off for now. Khorne fucked around with this message at 22:19 on Sep 19, 2023 |

|

|

|

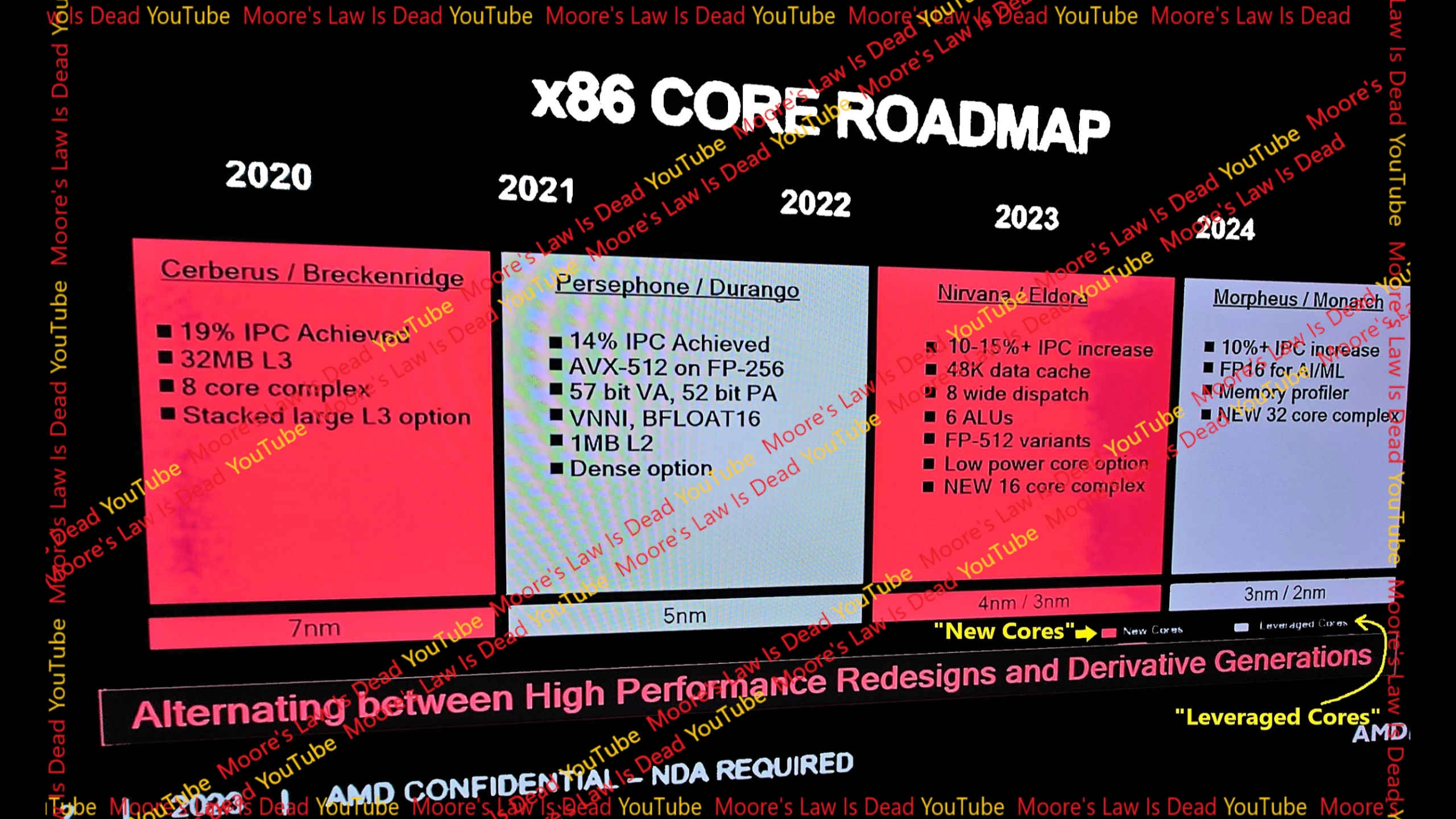

Obviously take everything MLID says with a grain of salt, but his AMD and Intel CPU leaks are generally accurate, and these slides are probably legit: https://videocardz.com/newz/amd-x86-core-roadmap-leaks-out-zen5-nirvana-zen6-morpheus-microarchitectures-detailed   MLID also suggests in that video that AMD might stack CCDs on top of the IOD for Zen 6 for direct silicon to silicon interfaces in order to cut down on die-to-die latency.

|

|

|

|

That would also be good for increasing the package height under the IHS as well, lowering the effective thickness of it and improving cooling?

|

|

|

|

Generally, I don't think die stacking has a tangible effect on package height. With or without 3D cache is a microscopic difference in height. I wonder if we'll see a double stacking situation with 3D cache on top of CCDs on top of the IOD. Or maybe they'll just put the L3 in the IOD.

|

|

|

|

If they're gonna double stack like that then I'd think they'll have to lower power/clocks (even with the process shrink). Or is the IOD big enough that you can put a CCD and the L3 die side by side on top of it instead of all 3 on top of each other? I suppose if the edges over hang they can just put a support underneath it if necessary. Can't be that hard or expensive to put a bit of aluminum under it if necessary. Probably would be worth it at that point to make the IHS into a vapor chamber instead of a slug of solid metal. But then I think doing something like that on the X Zen4 chips now would've been a good idea (and I wouldn't have minded a shim + exposed die instead).

|

|

|

|

Dr. Video Games 0031 posted:Generally, I don't think die stacking has a tangible effect on package height. With or without 3D cache is a microscopic difference in height. The L3 in the IOD (or in Intel's case, the interposer) underneath the compute chiplets is the path that Intel seems to be taking with Lunar Lake and/or Panther Lake. quote:As Gelsinger puts it, �[...] that particular type of technology isn't something that's part of Meteor Lake, but in our roadmap, you're seeing the idea of 3D silicon where we'll have cache on one die, and we'll have CPU compute on the stacked die on top of it, and obviously using EMIB that Foveros we'll be able to compose different capabilities.�

|

|

|

|

PC LOAD LETTER posted:If they're gonna double stack like that then I'd think they'll have to lower power/clocks (even with the process shrink). Flip that idea on its head, IMO. Stacking is real bad for power, but SRAM is low power density, so... why not make the IOD and the L3 die one big die? Lay things out so there's only SRAM directly underneath the CCDs, push all I/O functions to the edges where there's no overlap. The heatspreader would be in direct contact with the CCD, so this would actually offer better cooling of the CCD than today's X3D products. That does make the IO/cache die huge, but one advantage of it being mostly SRAM is that SRAM can have enough redundancy to be easily repairable to improve yield. This is just speculation on my part. No idea if the economics work, no idea if there's some other fatal problem with the idea. BTW, when there is a need to resolve overhang with a spacer, my guess is that package designers would use a blank piece of silicon rather than a metal like aluminum. This would keep the coefficient of thermal expansion of all the support materials for the die on top the same so that there's no bending forces as temperatures move around. e: if only I'd read Cygni's post before writing this one, lol BobHoward fucked around with this message at 09:26 on Sep 30, 2023 |

|

|

|

PC LOAD LETTER posted:If they're gonna double stack like that then I'd think they'll have to lower power/clocks (even with the process shrink). The advantage of stacking the cache is that there's basically no latency penalty. Having a separate memory die on the interposer/IOD would be much less useful for CPU performance but would be great for GPU bandwidth, if they're going that route with APUs.

|

|

|

|

BobHoward posted:why not make the IOD and the L3 die one big die? BobHoward posted:This would keep the coefficient of thermal expansion of all the support materials for the die on top the same so that there's no bending forces as temperatures move around. Arzachel posted:The advantage of stacking the cache is that there's basically no latency penalty. Having a separate memory die on the interposer/IOD would be much less useful for CPU performance but would be great for GPU bandwidth, if they're going that route with APUs.

|

|

|

|

Another reason you want cache on the IOD is that SRAM doesn't really scale on any process past 5nm. No point paying extra for super fancy expensive N3E/N2 silicon if the L3 takes the exact same amount of space. I think the IOD will be done on a (then) obsolete process like N4, making it a lot cheaper place to put the cache.

|

|

|

|

Don't stop until all space between CCDs and IODs is filled with fat SRAM stacks. Can you make the IHS out of SRAM?

|

|

|

|

karoshi posted:Don't stop until all space between CCDs and IODs is filled with fat SRAM stacks. Can you make the IHS out of SRAM? Terabytes of cache to make up for everything being programmed as a lovely web app.

|

|

|

|

|

| # ? May 18, 2024 06:39 |

|

Indiana_Krom posted:Terabytes of cache to make up for everything being programmed as a lovely web app. This is it. This is the way. Gentlement, we have the plan, now AMD need only execute on it~~

|

|

|