|

The nice thing about old CPU coolers is you can put them on the back of big COB leds for DIY blinding devices.

|

|

|

|

|

| # ? Jun 6, 2024 06:00 |

|

Rexxed posted:The nice thing about old CPU coolers is you can put them on the back of big COB leds for DIY blinding devices. Just use an ice pick like God intended

|

|

|

|

gradenko_2000 posted:it doesn't make sense for the 5700 to be the most expensive in the lot, because you're either getting a faster CPU with the X, or a working iGPU with the G The 5700 is the most expensive because it just came out and is being sold for msrp, while everything else has been around for a while. I'm sure it will drop fast.

|

|

|

|

Am I completely blind or does AMD adrenaline not have a "save the last 30/60 seconds of gameplay" hotkey?

|

|

|

|

Away all Goats posted:Am I completely blind or does AMD adrenaline not have a "save the last 30/60 seconds of gameplay" hotkey? I'm only using the software on an older RX580 but it has a Record & Stream section in the tabs at the top, and selecting that shows a subset of tabs under it with Settings. In there you can configure where to save videos, what to include (desktop, audio, mic, frame rate, etc) and then on the right side there's Instant Replay which when turned on can be set to save the last X seconds, the default is 60.

|

|

|

|

Rexxed posted:I'm only using the software on an older RX580 but it has a Record & Stream section in the tabs at the top, and selecting that shows a subset of tabs under it with Settings. In there you can configure where to save videos, what to include (desktop, audio, mic, frame rate, etc) and then on the right side there's Instant Replay which when turned on can be set to save the last X seconds, the default is 60. I did find those settings but couldn't figure out how to actually activate it. Turns out it was in Settings -> Hotkeys and the default is Ctrl+Shift+S. Thanks!

|

|

|

Away all Goats posted:Am I completely blind or does AMD adrenaline not have a "save the last 30/60 seconds of gameplay" hotkey? Even better, you can do custom lengths - what I've done is figure out the maximum size that can be written to my SSD in 1 second, and set it to just under that (which works out to ~4 minutes of AV1 at 1080p@60fps, but it'll be different for you). Then I use avidemux to cut the video to length at the appropriate keyframes (which it can do without reencoding, to upload to YouTube), and optionally two-pass reencode to a target file-size and downscale it to 720p@60fps H.264 (to inline it on Discord). BlankSystemDaemon fucked around with this message at 10:25 on Feb 17, 2024 |

|

|

|

|

I would check and make sure you can actually record video first. I was never able to get video recording to work in Adrenalin until https://www.amd.com/en/support/kb/release-notes/rn-rad-win-24-2-1-helldivers-2

|

|

|

Nalin posted:I would check and make sure you can actually record video first. I was never able to get video recording to work in Adrenalin until There's also an option to record the desktop, which is quite nice too.

|

|

|

|

|

Apparently Userbenchmark now requires a subscription to run their lovely benchmark suite more than once.

|

|

|

|

Combat Pretzel posted:Apparently Userbenchmark now requires a subscription to run their lovely benchmark suite more than once. Good, it's dogshit and should not be used by anybody with more than two brain cells to rub together.

|

|

|

|

Combat Pretzel posted:Apparently Userbenchmark now requires a subscription to run their lovely benchmark suite more than once. As if you needed any more reasons to ignore that horrible place.

|

|

|

|

On my 7900X, my understanding is the 64MB of L3 cache is split across the 2 CCDs. If a game (or application) doesn�t load cores across both CCDs, is the full L3 cache still being used?

|

|

|

|

Josh Lyman posted:On my 7900X, my understanding is the 64MB of L3 cache is split across the 2 CCDs. If a game (or application) doesn�t load cores across both CCDs, is the full L3 cache still being used? It is one cache, but some effort is likely made to keep stuff on one CCD from getting into the cache on the other CCD. If an application running on one CCD has something in the cache on the other CCD it will have to pay the latency and bandwidth penalty to retrieve it. The full cache can be used even by a single application, but there likely isn't much benefit from going over what fits in the local CCD. Indiana_Krom fucked around with this message at 22:44 on Feb 25, 2024 |

|

|

|

The full cache can't really be used by cores on one CCD, at least not in any beneficial sense. Going to the other CCD is as slow as going to RAM, it's only an option at all because it's necessary to maintain cache coherence. A 64MB cache AMD CPU is really best described as 2x32MB.

|

|

|

|

With the important note that this does not apply to all AMD CPUs. It's a large part of why some prefer the 7800X3D over the 7950X3D.

|

|

|

|

buffbus posted:With the important note that this does not apply to all AMD CPUs. It's a large part of why some prefer the 7800X3D over the 7950X3D. Yeah, it's why I specified 64MB. In my ideal world of them saying "2x32MB" or "96MB+32MB" we'd also be saved of all the dogshit articles saying "You could install your operating system in cache now!" because AMD markets Genoa-X as 1.152GB L3 instead of 12x96MB.

|

|

|

|

Indiana_Krom posted:It is one cache,

|

|

|

|

some rumors are suggesting that Zen5 is having a rough bring up and will launch later than originally expected. Su has a Computex keynote on June 3rd, which is def gonna be some sort of Zen5 announcement (along with AI AI AI AI AI), but dunno if we can expect that to be an actual product launch for desktop.

|

|

|

|

Tuna-Fish posted:No, it's not. The L3 is a victim cache of the L2:s of the cores that are in the same CCX. That is, the only way a line ever ends up in L3 is if it was first evicted by one of the local cores. The other CCD can read from the cache, but only for coherency, and this is not much faster than reading from main ram.

|

|

|

|

Cygni posted:some rumors are suggesting that Zen5 is having a rough bring up and will launch later than originally expected. Su has a Computex keynote on June 3rd, which is def gonna be some sort of Zen5 announcement (along with AI AI AI AI AI), but dunno if we can expect that to be an actual product launch for desktop. wait, Zen 5 already? christ, Lisa, take a breath what are we expecting out of it? hopefully better memory controller�

|

|

|

|

Josh Lyman posted:Would it make sense to think of my 7900X as 2x 6 core CPUs rather than 1x 12 core? If so, is Intel�s P+E architecture better about this type of thing? Intel's P+E architecture in client chips has a single L3 cache, yes. However, Intel's setup has its own big problems with caching, coherency, and inter-core bandwidth. When the E cores wake up it slows down the ring bus, slowing down how fast the P-cores are able to access L3 or memory: https://chipsandcheese.com/2021/12/16/alder-lake-e-cores-ring-clock-and-hybrid-teething-troubles/. Also, the E-cores share an L2 cache but have to synchronize through the L3 cache, meaning that core-to-core latency is worse for E cores that share an L2 cache than P-cores with each have independent L2 caches.

|

|

|

|

Subjunctive posted:wait, Zen 5 already? christ, Lisa, take a breath Zen 4 was released in 2022. Zen 5 is definitely coming this year. I don't think you should expect too much when it comes to memory speed. word is, AMD will only be bumping the "sweet spot" for overclocked memory to DDR5-6400. Which Zen 4 can already sorta do after one of last year's AGESA updates.

|

|

|

|

Tuna-Fish posted:No, it's not. The L3 is a victim cache of the L2:s of the cores that are in the same CCX. That is, the only way a line ever ends up in L3 is if it was first evicted by one of the local cores. The other CCD can read from the cache, but only for coherency, and this is not much faster than reading from main ram. Ah, that makes sense, been a while since I've read up on the arch.

|

|

|

|

Dr. Video Games 0031 posted:Zen 4 was released in 2022. Zen 5 is definitely coming this year. I don't think you should expect too much when it comes to memory speed. word is, AMD will only be bumping the "sweet spot" for overclocked memory to DDR5-6400. Which Zen 4 can already sorta do after one of last year's AGESA updates. I just want 32x4 at EXPO without worrying about my BIOS revision! (I�m going to upgrade regardless because I have a sickness.)

|

|

|

|

Subjunctive posted:wait, Zen 5 already? christ, Lisa, take a breath Literally exactly the same memory controller as Zen4. It's using the same IOD. The core is internally much wider, based on compiler cost model patches posted by AMD, but everything uncore (past L2) is the same as in Zen4. Subjunctive posted:I just want 32x4 at EXPO without worrying about my BIOS revision! Unless your sickness is very strong, if you already have Zen4 maybe hold on until Zen6. It's expected to come quite soon after Zen5, because it's supposed to use largely the same core, but with entirely new uncore/memory controller, using some fancy new way of integrating the dies.

|

|

|

|

Dr. Video Games 0031 posted:Zen 4 was released in 2022. Zen 5 is definitely coming this year. I don't think you should expect too much when it comes to memory speed. word is, AMD will only be bumping the "sweet spot" for overclocked memory to DDR5-6400. Which Zen 4 can already sorta do after one of last year's AGESA updates. one of MLIDs rumors was that AMD was pushing board vendors to certify this summers X870 boards (if they end up shipping them, it seems questionable) up to DDR5-8000, which which would still require you to go to 2:1 mode on the memory controller and will likely perform worse across the board with single CCD CPUs. but hey, marketing will like it! number go up!

|

|

|

|

Tuna-Fish posted:Unless your sickness is very strong, if you already have Zen4 maybe hold on until Zen6. It's expected to come quite soon after Zen5, because it's supposed to use largely the same core, but with entirely new uncore/memory controller, using some fancy new way of integrating the dies. I really appreciate your help with this, friend.

|

|

|

|

Zen 6 should be the last AM5?

|

|

|

|

Seamonster posted:Zen 6 should be the last AM5? supposedly yeah

|

|

|

|

Twerk from Home posted:When the E cores wake up it slows down the ring bus, slowing down how fast the P-cores are able to access L3 or memory: https://chipsandcheese.com/2021/12/16/alder-lake-e-cores-ring-clock-and-hybrid-teething-troubles/. This was fixed in Raptorlake. E cores and P cores are definitely better able to work on the same data than multi-CCD AMD, nothing you mentioned comes close to the cross-CCD penalty. It just turns out that as long as your CCX is large enough and your memory is uniform, you can just have NUCA without it really mattering too much for a lot of workloads. Cygni posted:one of MLIDs rumors was that AMD was pushing board vendors to certify this summers X870 boards (if they end up shipping them, it seems questionable) up to DDR5-8000, which which would still require you to go to 2:1 mode on the memory controller and will likely perform worse across the board with single CCD CPUs. 2:1 mode is faster than 1:1 mode for gaming when properly configured, even for single CCD CPUs (which you treat all AMD CPUs as for gaming). Running FCLK:UCLK at 1:1 is a large latency decrease and gaming performance increase, just like it was for AM4 era Zen CPUs, but you normally lose too much memory bandwidth to make it worth it. DDR5-8000 means you can run 4000:2000:2000 (MCLK:UCLK:FCLK), letting you still saturate your GMI link on bandwidth while providing lower latency than 1:1 mode.

|

|

|

|

there's some speculation that zen 6 will require a new socket, but there's no official word one way or another.

|

|

|

|

Dr. Video Games 0031 posted:there's some speculation that zen 6 will require a new socket, but there's no official word one way or another. *FM1/FM2 notwithstanding

|

|

|

|

Anime Schoolgirl posted:the last time they did a socket change that quickly* they undertook the absolute nightmare scenario of having to service and make interoperable CPUs for AM2 and AM3 at the same time, which was pretty funny in retrospect They also rolled out AM3+ very shortly afterward, which was basically a new socket.

|

|

|

|

BurritoJustice posted:2:1 mode is faster than 1:1 mode for gaming when properly configured, even for single CCD CPUs (which you treat all AMD CPUs as for gaming). Running FCLK:UCLK at 1:1 is a large latency decrease and gaming performance increase, just like it was for AM4 era Zen CPUs, but you normally lose too much memory bandwidth to make it worth it. DDR5-8000 means you can run 4000:2000:2000 (MCLK:UCLK:FCLK), letting you still saturate your GMI link on bandwidth while providing lower latency than 1:1 mode. huh ive never tried 7000+ myself, ive only got 6000 rated DDR5 and never really bothered beyond timings with my 7800X3D. i was just going off Buildzoid's numbers and opinions, but i might be wrong then.

|

|

|

|

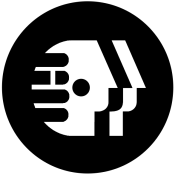

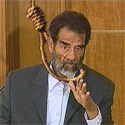

Cygni posted:huh ive never tried 7000+ myself, ive only got 6000 rated DDR5 and never really bothered beyond timings with my 7800X3D. i was just going off Buildzoid's numbers and opinions, but i might be wrong then. BZ doesn't believe in FCLK:UCLK sync being a thing at all despite it empirically showing benefit, he's repeatedly said in the past that there is no also reason to maintain the 2:3 ratio that AMD recommends but you can microbench it making a measurable difference in latency. I love a good opportunity to bring out my favourite infographic:  Aeryn didn't even hit 8000, only 7800, but you can still see it wins at everything. Dropping your FCLK to 1950MHz only loses out to the 2200MHz config in one test, because the bandwidth microbench is purely a GMI bench, so you can see the benefit of UCLK:FCLK match. You're still only looking at a 136.20/127.29 ≈ 7% mean performance increase over just using DDR5-6000 with buildzoid timings, lol.

|

|

|

|

Hmmm I�m running 2033MHz FCLK because of some Buildzoid rambling adjacent to his timings. I guess I should put it back to 2000MHz since I run RAM at 6000MT.

|

|

|

|

I need to update my BIOS and see if I can get this shithouse ASUS board above 5200 MHz on this 6000 MHz kit.

|

|

|

|

Combat Pretzel posted:Hmmm I’m running 2033MHz FCLK because of some Buildzoid rambling adjacent to his timings. I guess I should put it back to 2000MHz since I run RAM at 6000MT. It is still better to run higher FCLK than 2:3, but only if it's a good few straps higher. I'd either fiddle around finding the highest you can run, which will typically be in the range [2133,2200], or just drop back down to 2000.

|

|

|

|

|

| # ? Jun 6, 2024 06:00 |

|

Users who might want some advantage from overclocking but don't want to manually oc for funsies should just use the buildzoid timings. Despite him being wrong about a few things, his DDR5-6000 timings are highly compatible with Hynix kits and provide a tangible benefit over stock DDR5-6000 expo. There seems to be a bigger gap between buildzoid's timings and EXPO timings than there is between buildzoid timings and the DDR5-7800 config.

|

|

|